SPI协议学习

- 背景

- SPI协议时序

- SPI接口

- SPI时序

- SPI协议封装

- USB-SPI模块

- SPI数据格式定义

- FLASH数据格式参考

- 数据格式定义

背景

家里有一块ZYNQ开发板,经常想去写一写模块学习总线之类的东西,但是由于本人软件能力比较弱,ZYNQ的PS部分无论是Linux还是裸机用起来着实吃力,所以准备抛弃ARM部分,主要用PL部分。于是就想通过PC作为上位机,来访问内部的一些寄存器完成控制与调试。

常用的低速接口有UART、I2C、SPI等,从速率上看,SPI最佳。虽然是简单的调试,但是访问速度还是希望越快越好嘛。于是在某宝上淘来了USB转SPI的模块,准备通过SPI连到PL来完成简单的访问。

于是想写一个自定义的SPI SLAVE模块,方便逻辑简单的调试。

SPI协议时序

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是一种相对高速的,源同步通信总线。

SPI接口

SPI一般有4根信号线:

- SS_N:片选信号,拉低代表片选有效;SPI支持一对多传输,在有多个从设备的时候,主设备会到每一个从设备都有一个SS_N信号;

- SCLK:时钟信号,用于给从设备提供源同步时钟,仅在数据传输时才存在;

- MOSI:Master Out Slave In信号,主设备→从设备的数据信号;

- MISO:Master In Slave Out信号,从设备→主设备的数据信号;

上述这种数据定义是指的标准SPI模式,也就是Standard/Normal SPI模式。在某些对传输速率有要求的场合还会有Dual SPI模式和Quad SPI模式,常见于SPI NOR Flash这类的器件。

- Dual SPI:这种模式下MOSI与MISO信号变成了半双工,名称一般变为了SIO0、SIO1;因为一般Master与Slave不会同时输出数据,因此在Master发送数据的时候,两个信号均从Master传往Slave,在Slave回复数据的时候两根信号均从Slave传往Master,传输速率是标准模式的2倍。

- Quad SPI:这种模式下相比Dual SPI模式又多了两根依旧是半双工的数据线,即SIO2、SIO3,通常在SPI NOR FLASH上可能会和WP、HOLD管脚复用;传输模式与Dual SPI一样,因此传输速率是标准模式的4倍。

SPI时序

SPI的具体时序如下图所示:(图片源于《SPI协议(上)——基础介绍》)

SPI协议里有2个和时序相关的参数,我介绍一下自己的理解:

- CPOL:clk polar,时钟的极性,代表空闲状态下SCLK的状态;0:空闲为低;1:空闲为高;

- CPHA:clk phase,时钟的相位,代表第几个时钟沿是采样沿;0:第1个;1:第2个

主从设备均根据SCK对应的采样沿与数据输出沿进行数据的操作与传输。

SPI协议封装

由于SPI的接口时序相对简单,简单来说就是一个源同步的串口,具体传输规则的定义就自由度很大了。

USB-SPI模块

在某宝上买的这个USB-SPI模块看了下好像还挺高级,既支持当SPI Master还支持当Slave,还有I2C功能,当时看着功能挺多的就选了这个,以备不时之需。当然目前我需要用的功能就是PC端通过这个模块当MASTER。

看了下基本上都是以Byte为单位操作,一次性最多可以传输4096-byte也就是32768-bit的数据。那后面Slave的相关设计就保底按照这个规格来考虑了。

SPI数据格式定义

FLASH数据格式参考

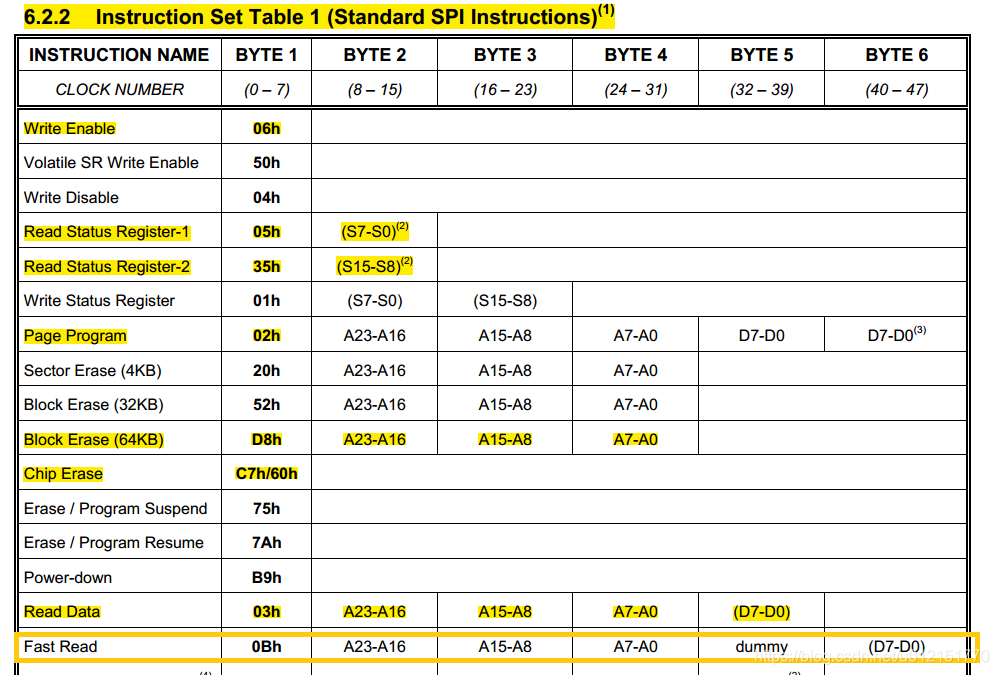

格式定义准备参考SPI FLASH的数据格式,这里是一份SPI FLASH的datasheet里的格式参考:

其中主要以 操作码 开头,后面再跟着不同操作的不同的数据格式

数据格式定义

之前自己开发过一个SPI的master和slave,也是进行简单的寄存器读写访问的,遇到了一个问题:设计帧格式的时候,没有考虑内部总线的时延,当时的帧格式是操作码+地址+数据,地址之后紧接着就是数据,这样在读操作的时候,收完地址后立马要去内部总线里去寻址读数据,紧接着就要立马输出读取到数据的第一个bit了,那么寻址返回数据的时间只有办个SCLK的周期,这个在一定程度上导致了SPI整体的速率上不去。

其中一个解决方案就是像上面那份FLASH的FAST READ一样,在发送完地址之后,定义一个byte的DUMMY字段,这样就给寻址返回数据预留了充足的时间。

但是我想为了提升效率,帧格式定义为了地址+操作码+数据,读写的区分定义在操作码的第1bit,这样也就预留了一定的时间给数据返回用。

整体数据格式的定义:

| 含义 | Byte | 位宽(bit) |

|---|---|---|

| 地址 | Byte0~Byte2 | 24 (简单调试24bit应该绰绰有余) |

| 操作码 | Byte3 | 8 |

| 数据 | 剩余Byte | 剩余数据(根据SS_N何时结束来判断) |

操作码含义的定义:

| 位域 | 内容 |

|---|---|

| bit[7] | 读写指示;0:读;1:写; |

| bit[6:4] | 操作位宽指示(指示总线有效数据位宽) 0:8-bit; 1:16-bit; 2:32-bit; 3:64-bit: 4:128-bit; 5:256-bit; 6:512-bit; 7:1024-bit |

| bit[3:0] | 保留字段 |

![[转]vimtutor——vim官方教程](/images/no-images.jpg)